DVB-GSE IPv4/IPv6 Encapsulator

Overview

High-throughput, low-latency encapsulator IP cores for building DVB-GSE systems. The IP Core Worx DVBGSE IP cores have been optimised for high performance, and also for DVB-S2/-T2/-C2 implementations that have strict resource/area constraints; for example, FPGA-based systems.

Features

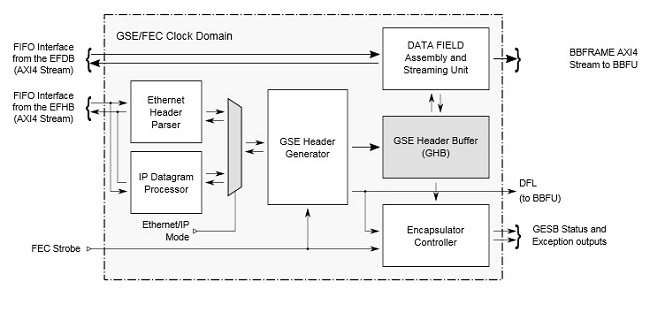

DVB-GSE encapsulator IP cores for IPv4/IPv6 network-layer traffic, and utilising AXI4-Stream interconnects for receiving IP packets, and for producing BBFRAME output.

- GSE fragmentation & encapsulation of IPv4/IPv6 packets

- Designed for high throughput1 and low latency

- Supports GSE packet header types for no labels, 6 byte labels, label reuse, for label-based filtering

- Parameterisable MTU’s and SRAM/buffer sizes

- Low (logic and SRAM) resource usage

- Support for both 16200b and 64800b BBFRAME’s, and all DATA FIELD sizes

- AXI4-Stream (8-bit) Interconnect

- Wishbone (SPEC B4) interface for control and packet/device statistics

- Includes BBFRAME generator, stream MUX & scheduler, and padding & scrambling cores

- Robust exception handling and with rapid recovery from exceptions (due to overflows & invalid input data)

- FPGA-proven with Xilinx and Microsemi devices

Deliverables

- Netlist or synthesisable RTL source code in VHDL

- Comprehensive verification test bench and vectors in VHDL

- User guides and documentation for integration & configuration

- Top-level entity for a CCM-only system, to aid with evaluation and rapid-prototyping

Performance

The following table shows the resource utilisation for various IP Core Worx DVB-GSE cores, when using Xilinx Vivado for synthesis, and targeting Xilinx ZYNQ devices. The designs satisfy the timing constraints at more than 160 MHz (ZYNC devices).

| Resource | IP_TO_GSE | GSE_TO_IP | ETH_TO_GSE | GSE_TO_ETH |

| LUT6 | 720 | 303 | 1086 | 638 |

| DFF | 411 | 228 | 655 | 455 |

| RAMB36 | 0.5 | 0.5 | 2 | 1.5 |

| DSP | 0 | 0 | 0 | 0 |

| BUFG | 1 | 1 | 1 | 1 |