Reciprocal Core

Overview

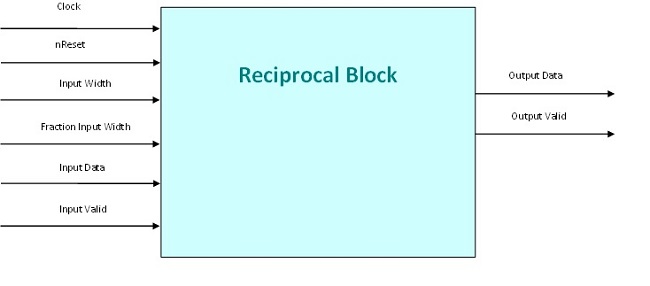

This is a configurable reciprocal DSP core for signal processing application on programmable logic devices.

The core operates on streamed data which is reciprocated (inverse value calculated) via a non-traditional, intelligent, innovative design. After an initial output delay equal to the bit width of the input plus 4 clock cycles, the output is also streamed out at a rate of one result per clock cycle.

This DSP engine is written in VHDL, capable of being used on any FPGA/ASIC architecture.

Features

Reciprocal Core is customizable and can be tailored to customer needs.

- Parameterisable input width

- Parameterisable fractional width input

- Very close reciprocal approximate output

- Area/Power efficient architecture

- Can be used in any hardware implementations where typically division may be avoided

- Fully synchronous design using only one clock

- No multipliers are used/required in the design

- Form factor only dependent on input bit width. Area grows at a rate less than linear input bit width.

- Silicon verified in multiple devices

- Optimized design allows customers to target cost efficient FPGAs.

- Can be tailored to customer needs

Deliverables

- Netlist or synthesizable RTL source code in VHDL

- Comprehensive verification test bench and vectors in VHDL

- Integration documentation and user guide

Performance

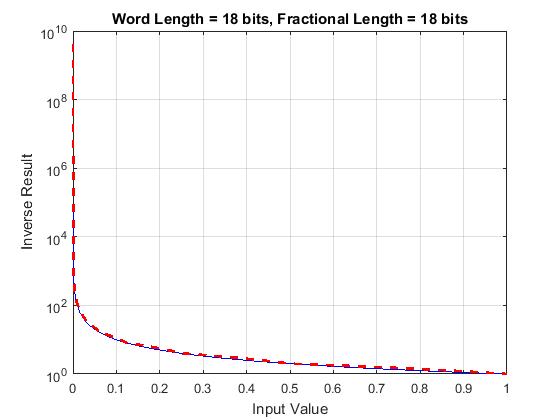

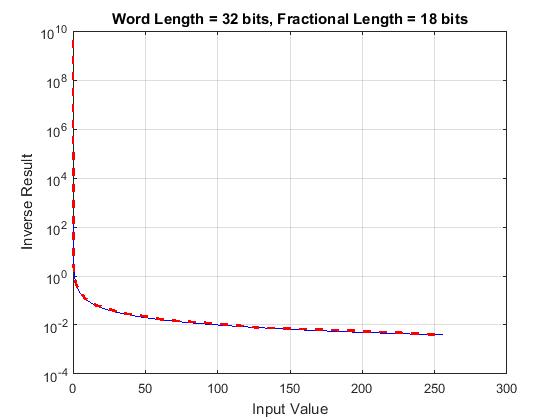

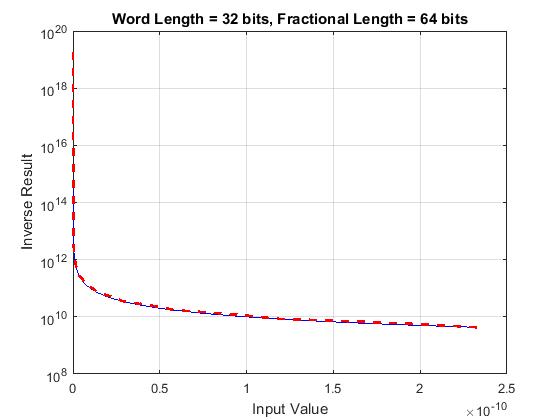

The following results compare the true floating-point reciprocal function (solid line) to the accuracy of the Reciprocal Core (dashed line) output. As can be seen from the graphs below, the output of the floating-point reciprocal function is a very close match to the output generated by the Reciprocal Core. Note that the input widths are parameterisable.

|

|

|

The following is the resource utilisation for a Xilinx Virtex6 FPGA.

| Input Width | Sices Used | Flip-Flops Used | Maximum Frequency |

| 18 bit | 267 | 576 | 346MHz |

| 32 bit | 397 | 551 | 389MHz |