Reed-Solomon Decoder Core

Overview

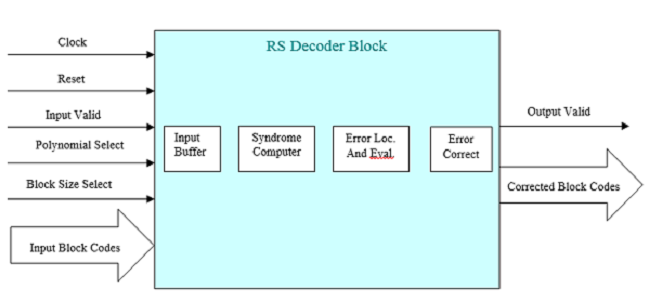

Reed-Solomon Decoder Core is Parameterisable and can also decode shortened and punctured codes.

Features

- Parameterisable primitive polynomial.

- Parameterisable symbol size (code block length)

- Parameterisable number of correctable errors

- Parameterisable input buffer size

- Decodes shortened and punctured codes

- Fully synchronous using single clock

- User friendly interface.

- Area efficient design

- Silicon verified in multiple devices

- Optimized for WMAN (802.16), DVB and other OFDM standards

Deliverables

- Netlist or synthesizable RTL source code in VHDL

- Comprehensive verification test bench and vectors in VHDL

- Integration documentation and user guide

Performance

The following is the resource utilisation summary on a Spartan-3E part for the WiMAX RS code (N=255,K=239,T=8) over GF(28) and generator polynomial X8+X4+X3+X2+1.

| Slices | Block RAMs | Flip Flops |

| 2410 | 3 | 3100 |

Note 1: Resource utilisation as reported by Xilinx ISE synthesiser. Utilisation may vary depending on application. Block RAM usage depends on input buffer size. Maximum core clock rate depends on application.

Specifications might change without notice. Information furnished by IPCoreWorx is believed to be accurate and reliable. However, no responsibility is assumed by IPCoreWorx for its use. All company and product names are trademarks or registered trademarks of their respective owners. All rights reserved. © 2014 IPCoreWorx.